专用集成电路设计 精准定制的技术基石

在当今信息技术飞速发展的时代,集成电路(IC)作为电子设备的心脏,其重要性不言而喻。其中,专用集成电路(ASIC,Application-Specific Integrated Circuit)设计,更是代表了集成电路领域内深度定制与高性能的尖端方向。与通用处理器(如CPU、GPU)不同,ASIC是为特定应用、特定算法或特定客户需求而量身定制的芯片。它通过牺牲通用性,在目标领域内实现了无与伦比的性能、能效和成本优势。

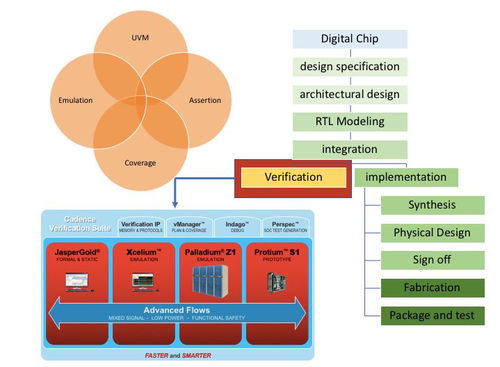

ASIC设计的核心流程是一个复杂而严谨的系统工程。它通常始于明确的设计需求与系统架构规划。设计团队需要与客户或系统工程师紧密合作,将功能、性能、功耗、面积和成本等指标转化为具体的电路架构方案。随后进入关键的硬件描述语言(如Verilog或VHDL)编码阶段,即通过代码来“描述”芯片的逻辑功能。

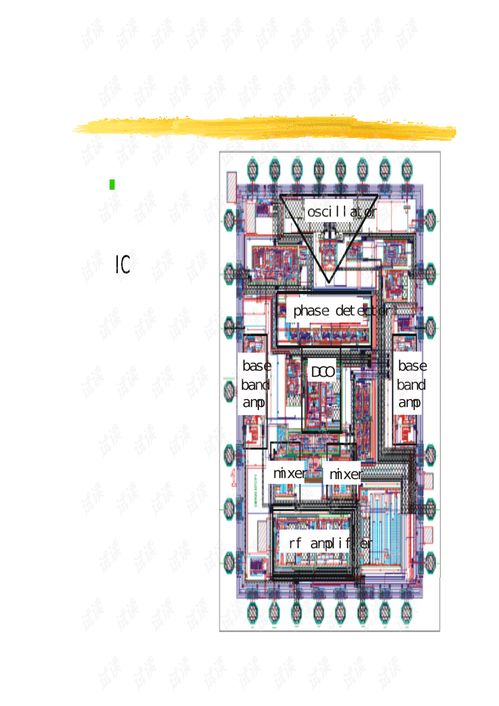

逻辑设计完成后,需要通过功能仿真进行验证,确保其行为符合预期。之后便是综合环节,将高级的硬件描述代码转换为由基本逻辑门(如与门、或门)组成的网表。这标志着设计从行为级进入到了门级。

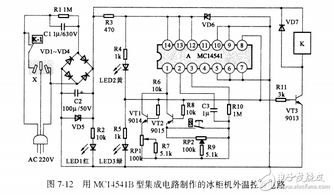

物理设计是ASIC流程中极具挑战性的一步。它包括布局(将逻辑单元放置在芯片版图上)、布线(用金属线连接这些单元)、时钟树综合(确保时钟信号同步到达各个单元)以及功耗和信号完整性分析。每一步都需要借助强大的电子设计自动化(EDA)工具,并反复迭代优化,以在性能、功耗和面积之间取得最佳平衡。

经过严格的验证和签核,设计数据将以GDSII等标准格式交付给晶圆厂进行流片制造。一颗ASIC从设计到量产,往往需要数月甚至数年的时间,并投入巨大的研发成本。因此,其应用场景通常集中在需求量足够大、或者对性能功耗有极致要求的领域。

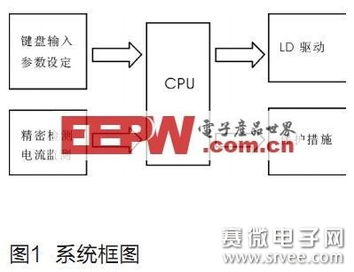

目前,ASIC已经渗透到我们数字生活的方方面面。最典型的例子是智能手机中的基带处理器、图像信号处理器(ISP)以及人工智能加速单元(NPU)。在数据中心,谷歌的TPU(张量处理单元)是专为机器学习定制的ASIC,极大地提升了AI训练和推理的效率。比特币矿机、汽车自动驾驶系统、高端网络路由器和各类工业控制设备中,也随处可见ASIC的身影。

随着5G、人工智能、物联网和自动驾驶的蓬勃发展,市场对计算效率的要求将越来越高。ASIC凭借其“专芯专用”的特性,必将在这些高增长领域扮演愈发关键的角色。先进工艺节点(如3纳米、2纳米)的演进、Chiplet(芯粒)异构集成技术的成熟,以及EDA工具的持续智能化,也将推动ASIC设计方法学不断革新,在追求更高性能、更低功耗的道路上持续突破,继续夯实其作为现代信息技术基石的牢固地位。

如若转载,请注明出处:http://www.yehongjy.com/product/70.html

更新时间:2026-04-16 08:17:23