零延时RS-485接口电路的设计与应用

在工业自动化、远程通信和分布式控制系统中,RS-485总线凭借其出色的抗干扰能力、长距离传输特性和多节点组网能力,已成为主流的串行通信标准之一。传统RS-485接口在收发切换时存在固有的传播延迟,这在某些对实时性要求极高的应用中(如高速运动控制、精准同步数据采集等)可能成为性能瓶颈。因此,设计一种‘零延时’或极低延迟的RS-485接口电路,成为了集成电路设计领域一个重要的研究方向。

一、传统RS-485接口的延时分析

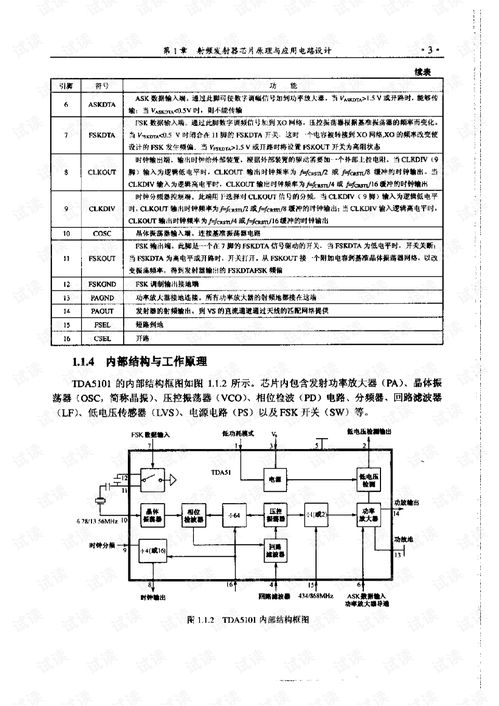

传统的RS-485接口芯片通常采用半双工模式,通过一个使能信号(DE/RE)控制收发状态的切换。延时主要来源于几个方面:

- 内部逻辑与驱动延时:芯片内部接收器比较器、驱动器开关电路的固有响应时间。

- 收发切换延时:从使能信号变化到驱动器或接收器完全进入有效状态所需的时间,这包括了芯片内部状态机的切换时间和输出级晶体管的开启/关断时间。

- 总线寄生电容充放电延时:在多节点、长电缆的应用中,总线等效电容较大,信号边沿的建立需要时间。

这些延时累积起来,在高速、双向频繁切换的通信中,会显著占用有效数据时间窗口,降低通信效率,甚至可能导致时序错误。

二、零延时RS-485接口电路的设计关键

实现‘零延时’并非绝对消除所有物理延迟,而是通过精妙的电路架构和设计技术,将关键路径的延迟最小化,并优化收发切换机制,使其对应用层近乎透明。核心设计思路包括:

- 自适应方向控制技术:摒弃外部MCU控制使能信号的模式,设计智能的方向检测与控制电路。该电路能实时监测本节点TXD引脚的状态变化,自动、快速地切换收发状态,从而省去了软件控制使能信号的指令执行与延时。这是实现‘零延时’概念的关键。

- 高速、低传播延迟的模拟前端设计:

- 驱动器:采用高压摆率(Slew Rate)的驱动电路,以快速建立总线电压。通过优化输出级晶体管尺寸和偏置,减少开启/关断时间。

- 接收器:设计高带宽、低失调的比较器,并采用滞回比较技术增强抗噪能力而不显著增加响应时间。输入级需具备高共模抑制比(CMRR)以快速识别总线上的微小差分信号。

- 创新的收发切换电路:设计专用的快速切换逻辑,将方向控制信号到驱动器/接收器使能的路径延迟降至最低。可能采用电流导引逻辑或经过特殊优化的CMOS逻辑。

- 工艺与版图优化:采用高性能的CMOS或BiCMOS工艺。在版图设计上,需精心布局匹配的差分对,减少寄生参数;缩短关键信号路径,并对大电流驱动部分进行充分的电源和地线设计,避免开关噪声引入额外延迟。

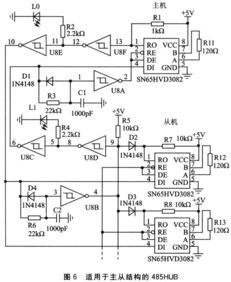

三、电路架构示例

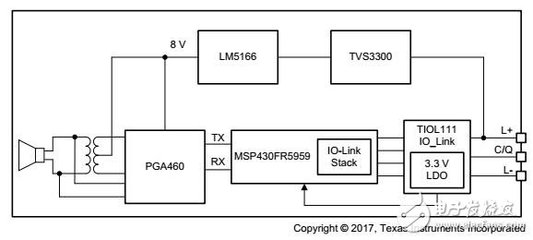

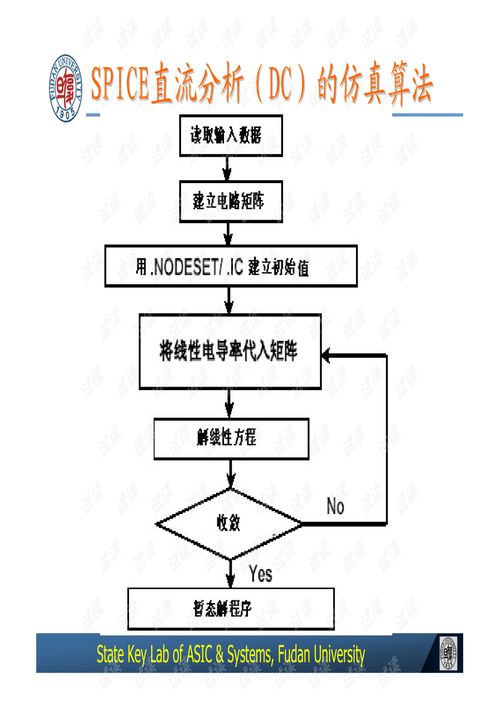

一种典型的零延时RS-485接口芯片内部框图包含:

- 智能方向控制器:核心逻辑单元,持续采样TXD,当其从空闲状态(如高电平)跳变时,立即在极短时间内(如几个纳秒)激活驱动器使能(DE)。当TXD恢复空闲并经过一个短暂的保护时间后,自动切换回接收使能(RE)状态。

- 超高速驱动器模块:接收TXD和DE信号,驱动A、B差分总线。

- 超高速接收器模块:在非发送状态下,始终监控总线,将差分信号转换为RXD单端信号。

- 失效保护与静电保护电路:确保总线开路、短路时输出确定逻辑电平,并集成高等级ESD保护(如±15kV HBM),不影响正常速度。

四、应用优势与场景

设计了零延时RS-485接口电路后,其应用优势十分明显:

- 提升有效数据吞吐率:几乎消除了切换死区时间,使得相同波特率下可用于传输数据的时间比例最大化,特别适用于高速率(如10Mbps及以上)通信。

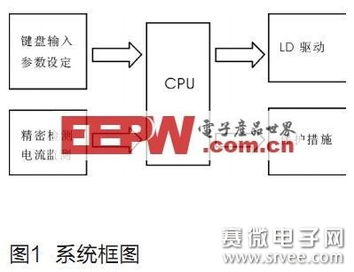

- 简化软件设计:无需MCU生成和控制使能信号,软件只需处理数据收发,降低了编程复杂度和CPU开销。

- 增强系统实时性:在闭环控制、多节点精准触发等场景中,更低的通信延迟意味着更快的系统响应速度。

主要应用领域包括:工业机器人伺服驱动网络、电力自动化设备的快速保护信号传输、测试测量仪器的同步数据采集系统、安防系统的高速视频数据控制总线以及任何对RS-485通信实时性有苛刻要求的场合。

五、与展望

零延时RS-485接口电路的设计,是传统标准在性能边界上的一次重要突破。它通过集成电路设计的创新,将模拟电路性能、数字逻辑智能和工艺版图优化深度融合,解决了实际应用中的延时痛点。随着工业4.0、物联网的深入发展,对通信网络的确定性和实时性要求将越来越高。此类接口电路可能会进一步与数字隔离技术、更强大的总线故障诊断与管理功能集成,形成更智能、更可靠、性能更极致的单芯片解决方案,持续为高要求的工业通信基础设施提供核心支撑。

如若转载,请注明出处:http://www.yehongjy.com/product/77.html

更新时间:2026-05-10 12:49:34