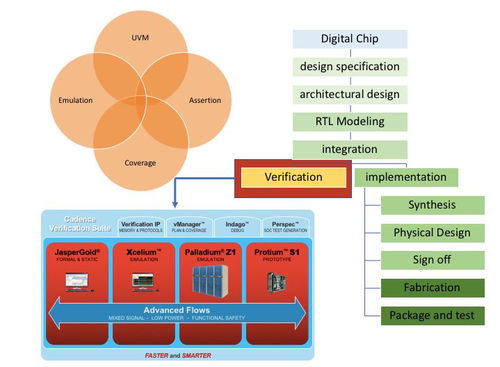

EDA集成电路设计实现流程详解

随着半导体工艺的不断进步,集成电路的复杂度与日俱增,纯粹依靠人工设计已无法满足现代芯片的需求。电子设计自动化(EDA,Electronic Design Automation)技术应运而生,成为支撑整个芯片产业的核心工具链。EDA工具通过一系列高度自动化的流程,将工程师的电路构思转化为可在硅片上制造的物理版图。一个典型的、基于EDA工具的集成电路设计实现流程,可以概括为从系统定义到最终流片的一系列严谨步骤。

第一阶段:设计输入与前端设计

此阶段的核心任务是将设计概念转化为可综合的电路描述。

- 系统规划与架构设计:确定芯片的功能、性能指标、功耗预算、封装形式等顶层规格。

- 寄存器传输级设计:使用硬件描述语言(HDL),如Verilog或VHDL,进行RTL(Register Transfer Level)编码。这一层级描述数据在寄存器之间的流动与转换,是功能设计的核心。

- 功能验证:通过仿真(Simulation)和形式验证(Formal Verification)等手段,确保RTL代码的功能完全符合规格书定义。此阶段通常使用如VCS、ModelSim等仿真工具和形式验证工具。

第二阶段:逻辑综合

这是连接前端设计与后端物理实现的关键桥梁。

- 逻辑综合:使用综合工具(如Design Compiler),将RTL代码映射到特定工艺库(由芯片代工厂提供)的门级网表。工具会根据设计约束(如时序、面积、功耗)进行优化。综合后生成的门级网表是后续所有物理设计的基础。

- 门级验证:对综合后的网表进行时序仿真和形式验证,确保功能在考虑门延迟后依然正确。

第三阶段:后端物理设计

此阶段目标是将门级网表转换为可供制造的物理版图(Layout)。

- 布图规划:规划芯片的宏观布局,确定核心功能模块、存储器、I/O单元等的位置和形状,规划电源网络和整体布线通道。

- 布局:将综合网表中的所有标准单元、宏模块等精确地放置到芯片的指定区域,优化线长、时序和拥塞。

- 时钟树综合:构建一个低偏斜、低功耗的全局时钟分布网络,确保时钟信号能同步、可靠地到达所有时序单元。

- 布线:根据逻辑连接关系,在布局好的单元之间进行实际金属连线。布线需遵守复杂的设计规则,并优化信号完整性、时序和功耗。

- 物理验证与签核:这是流片前的最后检查,至关重要。主要包括:

- 设计规则检查:确保版图完全符合代工厂的工艺制造规则。

- 版图与电路图一致性检查:确保物理版图与原始门级网表的电气连接完全一致。

- 时序签核:进行包含提取出的寄生参数(电阻、电容)的精确静态时序分析,确认芯片在所有工作条件下都能满足时序要求。

- 功耗签核:分析芯片的静态和动态功耗是否满足预算。

- 可靠性验证:包括电迁移、电压降等分析,确保芯片在长期工作下的可靠性。

第四阶段:流片与生产

- 数据交付:将最终通过所有验证的版图数据(通常为GDSII格式)交付给芯片代工厂。

- 掩膜版制作与晶圆制造:代工厂根据版图数据制作掩膜版,并在硅晶圆上通过光刻、刻蚀、离子注入等数百道工序进行制造。

- 封装与测试:制造完成的晶圆被切割成裸片,经过封装成为芯片,最后进行严格的成品测试,筛选出合格产品。

###

整个EDA设计流程是一个迭代、收敛的过程。后端物理设计的结果(如时序、面积)会反馈给前端,可能需要对RTL代码或约束进行修改优化。现代先进的EDA工具和流程(如高层次综合、物理综合)正不断模糊前端与后端的界限,提升设计效率。可以说,EDA是集成电路设计的“灵魂画笔”,它使得设计数亿乃至数百亿晶体管的复杂芯片成为可能,持续推动着信息技术的革命。

如若转载,请注明出处:http://www.yehongjy.com/product/82.html

更新时间:2026-04-14 18:32:30