便携式多功能数字分析仪的前放电路设计——集成电路设计视角

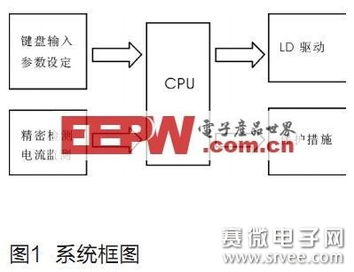

便携式多功能数字分析仪集信号采集、处理与分析于一身,广泛用于工业检测、环境监测及科研实验等领域。其性能的核心之一在于前端放大电路(前放电路),它直接决定了仪器对微弱信号的拾取能力、信噪比及动态范围。从集成电路(IC)设计的角度出发,设计一款高性能、低功耗、高集成度的前放电路,是实现仪器便携化与多功能化的关键。

一、 设计需求与挑战

便携式设备的前放电路设计需兼顾多项苛刻指标:

- 低噪声:需精确放大微伏级甚至纳伏级微弱信号,要求等效输入噪声电压密度极低,通常在nV/√Hz量级。

- 高输入阻抗:减少对被测信号源的负载效应,尤其在连接高阻抗传感器时至关重要。

- 低功耗:延长电池续航,要求电路在满足性能的前提下,工作电流尽可能小。

- 高共模抑制比(CMRR)与电源抑制比(PSRR):有效抑制环境共模干扰与电源波动,提升测量精度。

- 宽动态范围与可编程增益:适应不同幅值的输入信号,需集成可编程增益放大器(PGA)。

- 小型化与高集成度:通过IC设计将多级放大器、滤波、偏置等电路集成于单颗芯片,减少外围元件,缩小体积。

二、 集成电路架构设计

典型的集成化前放电路可采用以下架构:

- 仪表放大器(IA)核心:作为第一级,采用三运放或自稳零架构的集成仪表放大器,提供高输入阻抗、高CMRR及精确的差分放大。IC设计需优化内部匹配电阻网络,以获取高共模抑制和增益精度。

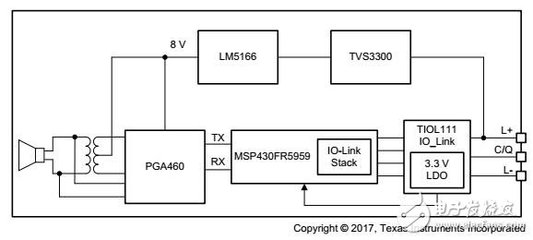

- 可编程增益级(PGA):紧随IA之后,通过开关电容网络或精密的模拟开关切换反馈电阻,实现多档位增益控制。数字接口(如SPI)集成于芯片内,便于微处理器控制。

- 滤波与驱动:集成抗混叠低通滤波器(可编程截止频率),并设计输出缓冲级以驱动后续ADC。

- 基准与偏置:芯片内部集成高稳定性带隙基准电压源与低噪声偏置电路,确保各级工作点稳定,降低对外部元件的依赖。

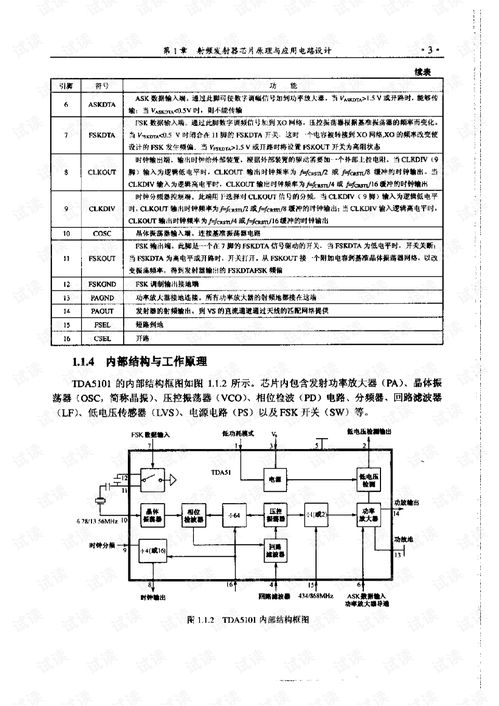

三、 关键IC设计技术

- 低噪声设计:选用低噪声的CMOS或BiCMOS工艺。在电路层面,输入级采用长沟道晶体管增大面积以降低1/f噪声;优化偏置电流,在功耗与热噪声间取得平衡;采用相关双采样(CDS)或斩波稳零(Chopper)技术,进一步抑制低频噪声与失调。

- 低功耗设计:采用亚阈值设计技术,使部分晶体管工作在亚阈值区,大幅降低静态电流;设计多电源域,对非关键路径进行动态电源管理;优化运放的摆率与带宽,满足信号保真度的同时最小化功耗。

- 高精度匹配设计:利用工艺的匹配特性,采用共质心、交叉耦合等版图技术,精心设计差分对与电阻阵列,确保增益精度和CMRR。

- 电源与抗干扰设计:在芯片内部增加去耦电容与稳压电路,提高PSRR;采用屏蔽、隔离环等版图技术,减少衬底噪声耦合与串扰。

四、 系统集成与测试考量

完整的IC设计需包含与后端数字处理器的接口(如数字控制逻辑、状态寄存器)。芯片在流片后,需进行严格的测试,包括噪声谱密度测量、增益误差、非线性度、CMRR/PSRR测试以及全温度范围内的性能验证。

结论:从集成电路视角设计便携式数字分析仪的前放电路,是一个系统工程,需在工艺选择、电路架构、版图实现与系统集成等多个层面进行深度优化。通过高度集成的IC方案,能够实现前放电路在性能、功耗、体积和可靠性上的最佳平衡,从而为便携式多功能数字分析仪提供强大的“感官”核心,推动其在更广泛领域的应用。

如若转载,请注明出处:http://www.yehongjy.com/product/78.html

更新时间:2026-05-10 02:33:13