CMOS模拟集成电路版图设计第五章 Calibre验证文件详解与集成电路设计流程

集成电路设计是一个高度复杂且严谨的过程,其中版图设计完成后,必须通过一系列严格的物理验证才能确保芯片功能的正确性与制造的可靠性。Calibre作为业界领先的物理验证工具,其验证文件的编写与执行是连接设计与制造的关键桥梁。本章将深入探讨Calibre验证文件的基础、核心方法及其在集成电路设计流程中的关键作用。

一、Calibre验证文件基础:DRC、LVS与ERC

Calibre验证主要包含三大核心部分:设计规则检查(DRC)、版图与电路图一致性检查(LVS)和电气规则检查(ERC)。

- 设计规则检查(DRC):这是物理验证的首要步骤。DRC文件(通常以

.calibre或.drv为扩展名)由代工厂(Foundry)提供,其中定义了芯片制造工艺所必须遵守的所有几何规则。例如,晶体管的最小沟道长度、金属线的最小宽度和间距、接触孔的大小及覆盖范围等。Calibre DRC工具会根据这些规则,自动检查版图中所有图形层是否存在违反规则的情况,并生成详细的错误报告。确保DRC Clean是版图流片(Tape-out)的基本前提。

- 版图与电路图一致性检查(LVS):LVS验证旨在确保实际绘制的版图(Layout)与电路设计原理图(Schematic)在电气连接上完全一致。LVS验证文件(通常包含

.calibre、.lvs等文件)会提取版图中的器件(如MOS管、电阻、电容)和连接关系(Netlist),并与原理图网表进行比对。LVS验证不仅检查器件类型、数量是否匹配,更重要的是验证所有节点的连接关系是否正确。LVS通过是保证芯片功能正确的关键。

- 电气规则检查(ERC):ERC主要检查版图中潜在的电气问题,这些问题可能不违反几何设计规则,但会导致电路失效。例如,检查是否存在浮空的栅极(Gate)、电源和地之间是否短路、衬底连接是否正确等。ERC规则通常也包含在LVS或独立的规则文件中,是DRC和LVS的重要补充。

二、Calibre验证文件的核心方法与编写要点

- 规则文件结构:典型的Calibre规则文件采用层次化的语法结构。它通常包括头文件声明、层定义、规则主体等部分。层定义将版图数据(GDS/OASIS文件中的层号)映射到Calibre内部用于运算的逻辑层。规则主体则使用丰富的命令和运算符(如AND、OR、NOT、SIZE、ENCLOSE等)来描述复杂的几何与电气约束。

- 层操作与衍生层:验证的核心是对图形层进行逻辑运算,生成“衍生层”。例如,要检查金属1(M1)与多晶硅(Poly)的最小间距,需要先定义M1层和Poly层,然后使用

SPACE命令对两者进行间距检查。通过组合不同的层操作,可以构建出非常复杂的检查场景,如检查天线效应(Antenna Rule)、阱间距(Well Proximity)等。

- 器件识别与属性提取:在LVS文件中,最关键的部分是“器件识别”模块。它通过一系列层操作,从版图中“切割”并识别出一个个独立的器件。例如,一个NMOS管可以通过有源区(Active)、多晶硅(Poly)以及N型注入层(N_imp)的交叠来定义。识别后,还需要提取器件的属性,如MOS管的宽(W)和长(L)。这些信息将与原理图网表中的器件参数进行比对。

- 连接关系提取:LVS的另一核心是提取连接关系。通过定义连接层(如金属层、接触孔/通孔层),Calibre可以自动生成版图的电气连接网表。验证文件需要明确定义哪些层之间通过接触孔相连,从而构建出完整的导电通路。

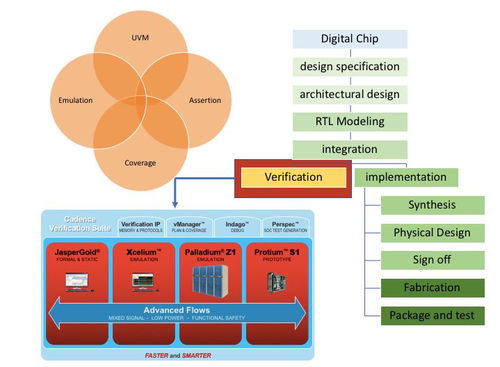

三、验证流程与集成电路设计整合

在完整的集成电路设计流程中,Calibre验证并非一次性工作,而是与版图设计迭代并行的过程。

- 交互式验证(Online Verification):现代版图设计工具(如Cadence Virtuoso)通常与Calibre深度集成,支持在绘制版图的同时实时或快速进行DRC和LVS检查。这允许设计者及时发现并修正错误,极大提高了设计效率。

- 签核验证(Sign-off Verification):在版图最终完成后,需要进行全面、严格的“签核”验证。这通常是离线的、批处理式的完整运行,确保在所有工艺角(Corner)下,DRC、LVS和ERC都完全通过。只有签核验证通过,版图数据才能交付给代工厂进行掩模制作。

- 与寄生参数提取的协同:物理验证通过后,通常还需要使用Calibre xRC等工具从验证后的洁净版图中提取寄生电阻和电容(PEX),生成带寄生参数的电路网表。将此网表反标(Back-annotate)到电路仿真器中,进行后仿真(Post-layout Simulation),以验证版图寄生效应是否影响电路性能(如速度、功耗、噪声等)。这是确保设计成功的关键一步。

四、

Calibre验证文件是连接CMOS模拟集成电路设计与制造的“法律文书”和“质量检测标准”。掌握其基础语法、理解DRC、LVS、ERC的核心原理与方法,并熟练将其融入迭代设计流程,是每一位模拟版图工程师和芯片设计者的必备技能。一个洁净、验证通过的版图,是芯片从设计蓝图变为物理实体的坚实保障。通过严谨的物理验证,才能最大程度地降低流片风险,提高芯片的一次成功率。

如若转载,请注明出处:http://www.yehongjy.com/product/64.html

更新时间:2026-04-16 17:42:16