基于ISO/IEC 14443 A协议的无源电子标签数字集成电路设计

随着物联网、智能识别和供应链管理等领域的飞速发展,近场通信技术,特别是基于ISO/IEC 14443 A协议的非接触式识别系统,已成为现代生活的关键技术之一。作为该系统的核心,无源电子标签(常称为PICC,即邻近耦合卡)无需内置电源,通过从读写器(PCD)发射的射频场中获取能量并完成通信。其数字集成电路的设计,直接决定了标签的性能、成本与可靠性。本文旨在探讨基于14443 A协议的无源电子标签数字集成电路的关键设计考量与实现方案。

一、系统架构概述

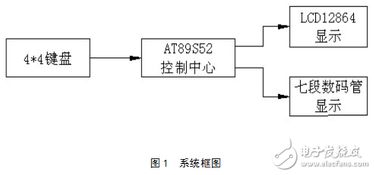

一个完整的无源电子标签数字集成电路,通常包含以下几个核心模块:

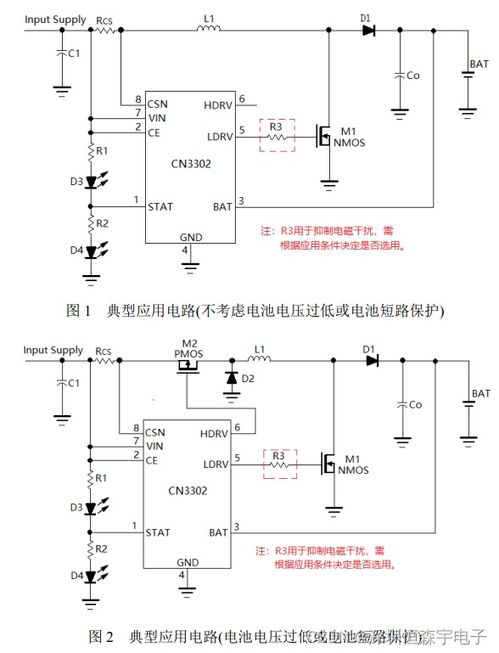

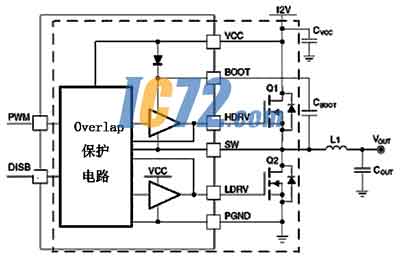

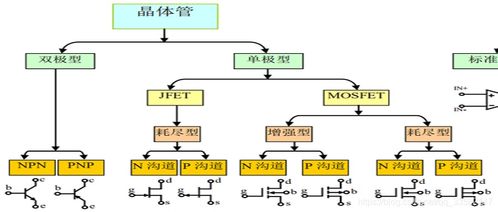

- 射频前端与电源管理单元:负责从天线接收的13.56MHz载波中通过整流、稳压和上电复位电路,为整个芯片提供稳定的工作电压和可靠的启动信号。这是标签工作的能量基础。

- 时钟提取与恢复单元:从读写器调制信号(100% ASK调制)中提取出副载波时钟,并再生出系统所需的工作时钟。

- 解调器:对读写器发送的经过改进米勒编码的指令数据进行解调,将其转换为数字基带信号。

- 数字基带处理核心(本文重点):这是标签的“大脑”,负责协议处理、数据编解码、状态机控制、防碰撞算法执行以及存储器访问控制。

- 调制器与负载调制单元:根据协议,通过控制天线的负载(通常采用副载波负载调制),将标签的响应数据(曼彻斯特编码)发送回读写器。

- 非易失性存储器接口:通常为EEPROM或FRAM,用于存储唯一的标识符(UID)、应用数据及安全密钥等。

二、数字基带处理核心的设计要点

数字集成电路设计是整个标签设计的灵魂,需严格遵循14443 A协议,并实现低功耗、小面积和高可靠性。

1. 协议状态机设计:

数字核心需实现协议规定的完整状态机,通常包括:断电(POWER-OFF)、空闲(IDLE)、就绪(READY)、防碰撞(ANTICOLLISION)、激活(ACTIVE) 以及 停止(HALT) 状态。状态机的转换由读写器指令(如REQA、WUPA、SELECT、HLTA等)精确触发。设计时需确保状态转换逻辑清晰、无歧义,并能正确处理异常情况。

2. 防碰撞算法实现:

14443 A协议采用基于比特冲突检测的时隙ALOHA防碰撞算法。数字核心必须能够执行标准的防碰撞循环:接收ANTICOLLISION命令,根据自身UID的对应比特位进行响应,并在检测到冲突时(通过读写器返回的冲突标志)更新其内部搜索指针。这要求设计高效的比特比较与序列管理逻辑。

3. 编解码模块:

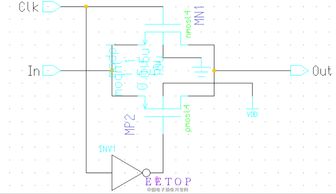

* 解码:需实现对读写器发送的改进米勒编码(每位数据有固定的脉冲模式)的同步与解码,并完成奇偶校验。

- 编码:需实现标签响应的曼彻斯特编码生成,确保时序符合协议规定的位帧格式(et.u)。

4. 低功耗设计技术:

由于标签完全依赖射频供电,功耗是设计的首要约束。在数字电路中可采用以下技术:

- 门控时钟:为不工作的模块关闭时钟,大幅降低动态功耗。

- 多电压域与电源门控:对非关键路径或待机模块使用更低电压或完全关断供电。

- 优化的有限状态机:使用格雷码或One-hot编码,减少状态跳变时的开关活动。

- 系统级休眠策略:在空闲或停止状态,关闭绝大多数数字逻辑,仅保留少数唤醒检测电路。

5. 安全与认证模块(可选但日益重要):

对于安全要求较高的应用(如支付、门禁),数字核心需集成加密协处理器,以支持如ISO/IEC 14443-4中定义的加密传输或专有的安全认证协议(如MIFARE的CRYPTO1)。这包括实现DES/3DES、AES等算法的硬件加速器。

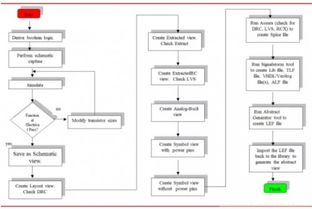

三、集成电路设计流程与实现考虑

- RTL级设计与验证:使用硬件描述语言(如Verilog HDL)完成上述各模块的寄存器传输级设计。验证是重中之重,需搭建完整的仿真测试平台,模拟读写器与标签的交互,覆盖协议的所有正常和异常用例。

- 逻辑综合与优化:使用标准单元库,在给定的时序、面积和功耗约束下,将RTL代码转换为门级网表。此时需特别关注关键路径(如编解码、防碰撞处理)的时序收敛。

- 物理设计:包括布局规划、时钟树综合、布局布线、电源网络设计等。对于无源标签芯片,面积成本极其敏感,需采用紧凑的布局。要确保电源网络能够稳定地配送从射频前端获取的微弱电能。

- 后仿真与签核:提取布局布线后的寄生参数,进行带有时序信息的门级仿真和静态时序分析,确保芯片在工艺角、电压和温度变化下仍能可靠工作。

- 测试与可测性设计:在生产前,需在芯片中插入扫描链等DFT结构,以便对制造出的芯片进行故障测试,保证良率。

四、挑战与发展趋势

- 超低功耗与高灵敏度:为了延长通信距离或降低读写器发射功率,需要不断优化数字电路的功耗和唤醒灵敏度。

- 更高的安全性:应对日益复杂的攻击手段,需要设计更强大的物理不可克隆功能(PUF)和抗侧信道攻击的加密模块。

- 系统级封装与柔性电子:将数字核心与射频前端、存储器甚至传感器集成于单个芯片或采用SiP技术,并探索在柔性衬底上的实现,以拓展其在可穿戴设备、智能包装等新领域的应用。

结论

基于ISO/IEC 14443 A协议的无源电子标签数字集成电路设计,是一个融合了通信协议、数字电路设计、低功耗技术和半导体工艺的综合性工程。其核心在于用最精简、最可靠的硬件逻辑,严格、高效地实现协议栈的全部功能。随着工艺进步和应用需求的深化,该领域的设计将继续朝着更低功耗、更高集成度、更强安全性和更广泛应用场景的方向发展。

如若转载,请注明出处:http://www.yehongjy.com/product/43.html

更新时间:2026-04-14 10:01:29