基于数字集成电路技术的LCD数码显示器设计与实现

摘要:随着信息显示技术的飞速发展,LCD数码显示器因其功耗低、体积小、可靠性高等优点,在工业仪表、家用电器、便携设备等领域得到了广泛应用。本文聚焦于采用数字集成电路技术进行LCD数码显示器的核心设计,详细阐述了从系统架构、数字逻辑设计到集成电路实现的全过程。

1. 引言

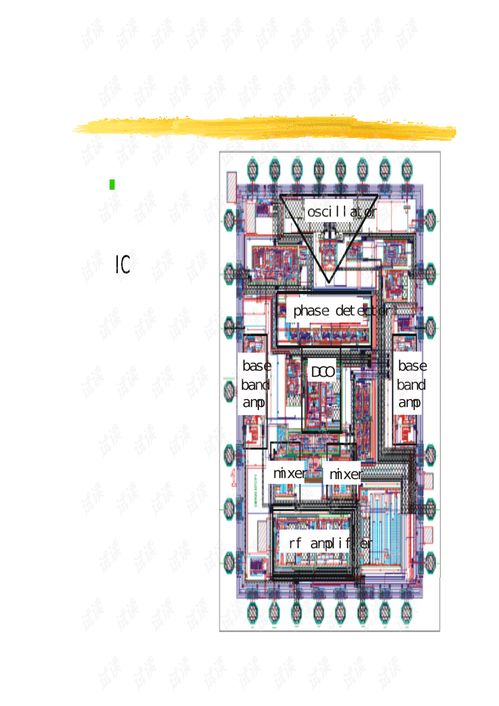

LCD数码显示器是一种利用液晶的电光效应来显示数字、字符或简单图形的显示器件。传统的驱动方式可能涉及分立元件或通用逻辑芯片,导致系统复杂、体积庞大。而基于专用数字集成电路(ASIC)或可编程逻辑器件(如CPLD、FPGA)的设计,能够将控制逻辑、驱动电路和时序生成高度集成,显著提升系统的集成度、可靠性和性能。

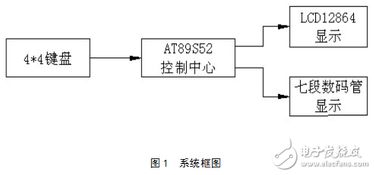

2. 系统总体架构设计

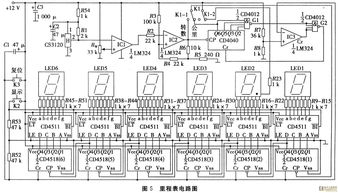

一个典型的基于数字IC技术的LCD数码显示系统主要由以下几部分构成:

- 显示数据接口模块:负责接收来自微处理器或其它数字系统(如计数器、寄存器)的BCD码或其它编码的显示数据。

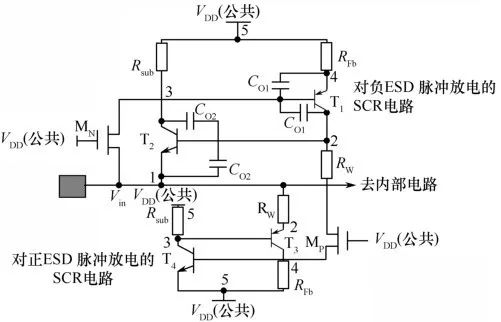

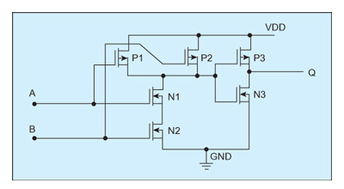

- 控制与译码逻辑模块:这是设计的核心。它将输入的显示数据(如4位BCD码)转换为对应于LCD七段(或更多段,如带小数点的八段)笔画的段码。生成LCD驱动所需的交流波形控制信号,以防止液晶直流极化损坏。

- 时序生成模块:产生系统所需的工作时钟,以及控制数据锁存、刷新显示的时序信号。

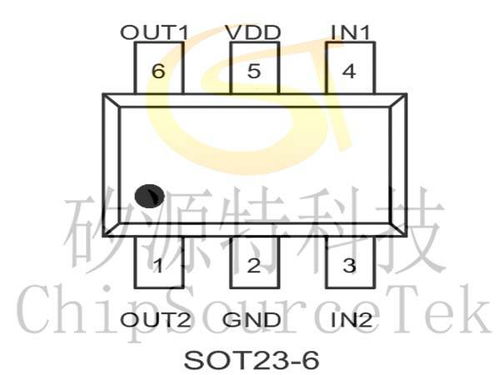

- 驱动输出模块:将译码逻辑产生的低压数字信号,转换为能够驱动液晶段点亮或熄灭的、具有一定电压幅值的交流方波信号。

- 核心数字集成电路设计

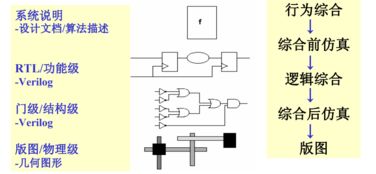

- 译码器设计:采用硬件描述语言(如Verilog HDL或VHDL)设计一个七段LCD译码器。该译码器的真值表需考虑LCD的驱动特性:当某段需要点亮时,其驱动信号与背板(COM)信号应为反相的交流方波;当需要熄灭时,则为同相的交流方波。因此,译码器输出并非简单的‘1’或‘0’,而是代表相位状态的逻辑值。

- 时序与控制逻辑设计:设计一个状态机或计数器,用于产生背板(COM)的交流方波(通常为占空比1:1的方波),并确保段驱动信号(SEG)与之同步。关键是要确保驱动电压的直流分量为零。

- 多位数动态扫描设计:为了驱动多位LCD数码管并减少引脚数量,常采用动态扫描(时分复用)技术。设计一个扫描计数器,循环选通每一位的公共端(COM),同时将对应位的段码数据同步送到段驱动线上。这要求译码和驱动模块具备数据锁存和快速切换能力。

- 集成电路实现与验证

- 仿真验证:使用EDA工具(如ModelSim)对HDL代码进行功能仿真和时序仿真,验证译码正确性、交流驱动波形以及动态扫描逻辑。

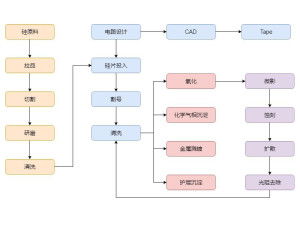

- 综合与实现:将已验证的HDL代码通过逻辑综合工具,映射到目标工艺库(对于ASIC)或特定的FPGA/CPLD器件中。优化面积和时序。

- 物理设计与输出:对于ASIC设计,需要进行布局布线、版图设计、设计规则检查(DRC)和电路规则检查(LVS)。最终生成用于芯片制造的GDSII文件。对于FPGA,则生成配置文件。

- 测试:制作测试电路板,将编程后的FPGA或制成的ASIC芯片与LCD面板连接,进行实际显示测试,验证其功能与可靠性。

- 优势与挑战

- 优势:高度集成化,系统体积小,功耗低;设计灵活,可通过修改HDL代码快速适配不同显示内容或LCD型号;性能稳定,抗干扰能力强;便于批量生产,成本可控。

- 挑战:需要精确的时序设计以确保LCD的交流驱动和动态扫描无闪烁;对驱动电压的精度和对称性有要求;在高位数或多路复用情况下,需平衡扫描频率与显示亮度的关系。

6. 结论

基于数字集成电路技术设计LCD数码显示器,是现代电子系统小型化、智能化的必然选择。通过自顶向下的设计方法,利用硬件描述语言和先进的EDA工具,可以高效、可靠地完成从逻辑设计到物理实现的全过程。这种设计不仅提升了产品性能,也为实现更复杂的显示控制(如字符点阵LCD驱动)奠定了坚实的技术基础。随着低功耗芯片技术和更先进显示技术的融合,此类集成化显示解决方案将拥有更广阔的应用前景。

如若转载,请注明出处:http://www.yehongjy.com/product/57.html

更新时间:2026-04-14 10:03:34